Q. A standard CMOS inverter is designed with equal rise and fall times (β𝑛 = βp). If the width of the pMOS transistor in the inverter is increased, what would be the effect on the LOW noise margin (𝑁𝑀𝐿) and the HIGH noise margin 𝑁𝑀𝐻?

A. 𝑁𝑀𝐿 increases and 𝑁𝑀𝐻 decreases.

B. 𝑁𝑀𝐿 decreases and 𝑁𝑀𝐻 increases.

C. Both 𝑁𝑀𝐿 and 𝑁𝑀𝐻 increase.

D. No change in the noise margins.

Ans: NML increases and NMH decreases

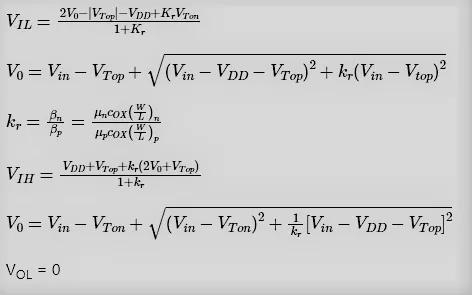

Solution:

The behavior of the CMOS inverter for static conditions of operation is described by the voltage transfer characteristics (VTC) and for dynamic operation, the condition is described by the time response during switching conditions. VOH = VDD